進口冷鏈食品外包裝頻繁檢出新冠病毒核酸陽性,引發(fā)公眾廣泛擔憂。進口冷鏈食品還能安全食用嗎?如何科學防護?記者深入上海冷庫第一線探訪,并結(jié)合復旦大學附屬華山醫(yī)院感染科主任張文宏教授的專業(yè)建議,為您提供清晰指引。

一、直擊現(xiàn)場:上海冷庫的嚴密防線

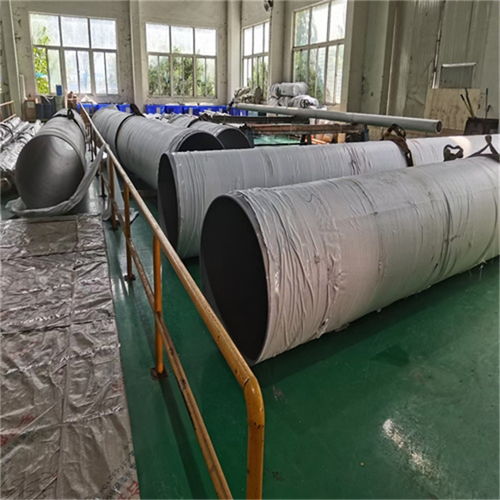

在上海多個大型進口冷鏈食品集中監(jiān)管倉,記者看到,從港口入關的集裝箱貨柜需首先進入這一指定區(qū)域。所有貨物均實行“逢進必檢”,即對每批進口冷鏈食品的外包裝、內(nèi)包裝及食品本身進行采樣和核酸檢測。只有檢測結(jié)果全部為陰性的批次,才能獲得《出庫證明》,進入市場流通。裝卸、采樣、消殺等一線工作人員,是防護的重中之重。他們嚴格按照規(guī)范,穿著全套的特種勞動防護用品,包括連體防護服、防護面屏、N95口罩、防水靴套和雙層手套等,確保與貨物“零接觸”或全流程防護。

二、專家解讀:風險分析與食用建議

針對公眾最關心的“能否食用”問題,張文宏醫(yī)生團隊進行了多次科普解讀。核心觀點如下:

- 風險所在:目前檢測到的病毒陽性主要集中在外包裝,病毒通過冷鏈運輸存活的可能性增加,但“物傳人”的感染風險總體低于“人傳人”。

- 科學看待:“檢測陽性”不等于“具有傳染性”。核酸片段的存在,就像“病毒的殘骸”,不一定代表有活病毒。即使有活病毒,要達到足以使人感染的劑量,并通過接觸、再接觸口鼻眼等黏膜的方式實現(xiàn)傳播,概率也相對較低。

- 關鍵建議:張文宏醫(yī)生強調(diào),對于普通消費者,通過正規(guī)渠道購買的進口冷鏈食品,經(jīng)過國家層層檢疫,安全是有保障的。關鍵在于做好后續(xù)的個人防護與規(guī)范處理。

三、消費者安全操作指南

在流通和消費末端,安全掌握在自己手中。專家和疾控部門建議:

- 選購時:前往正規(guī)超市或市場,注意查看冷鏈食品的檢疫證明。佩戴好口罩,保持社交距離,優(yōu)先使用掃碼支付。

- 處理時:

- 保持清潔:觸碰后立即洗手,避免不潔手觸摸口鼻眼。

- 生熟分開:使用專用刀具和案板處理生鮮,避免交叉污染。

- 充分煮熟:新冠病毒對熱敏感,70攝氏度以上持續(xù)幾分鐘即可滅活。因此,將食物徹底燒熟煮透是安全食用的最有效方法。

- 包裝處理:對外包裝可用75%酒精或含氯消毒劑擦拭消毒,處理完畢后,妥善丟棄外包裝并再次洗手。

四、產(chǎn)業(yè)鏈的守護:特種勞動防護用品的關鍵角色

在整個防控鏈條中,從港口、冷庫到運輸、市場,一線工作人員是高風險人群。他們所使用的特種勞動防護用品,如符合國標的高等級防護服、防護口罩、護目鏡等,構(gòu)成了阻斷病毒傳播的堅實物理屏障。這些用品的規(guī)范銷售、配備和使用,不僅是企業(yè)安全生產(chǎn)的必然要求,更是維護整個食品供應鏈安全、保障公共衛(wèi)生的基石。監(jiān)管部門也持續(xù)加強對相關勞動防護用品質(zhì)量與流通環(huán)節(jié)的監(jiān)督檢查。

結(jié)論

面對進口冷鏈食品,我們無需過度恐慌,但必須保持科學警惕。國家的集中監(jiān)管、一線的嚴密防線、專家的理性建議,共同構(gòu)建了多層次的安全網(wǎng)。作為消費者,通過正規(guī)渠道購買,并嚴格踐行“清潔、分離、煮熟”的廚房安全原則,就能有效保護自己和家人。而保障整個鏈條運轉(zhuǎn)安全的,正是無數(shù)一線工作者和他們身上那套可靠的特種勞動防護用品所代表的專業(yè)與責任。